TEM samples such as semiconductor devices, fuel cells, batteries and magnetic media are often prepared on E-chips using focused-ion beam (FIB) techniques. While this sample preparation technique is faster and more versatile than conventional polishing techniques, it can be challenging and several steps are involved. This sample preparation guide steps through in-situ liftout methods, ex-situ lift-out methods, addresses Pt contamination concerns, and discusses how to make electrical connections, so you can successfully prepare samples using FIB.

### In-Situ Lift-Out Method Using Omniprobe

The steps described in this method are optimized for the Omniprobe micromanipulator system. Micromanipulator systems from other manufacturers may or may not work using this method.

### 1. Thin to Electron Transparency

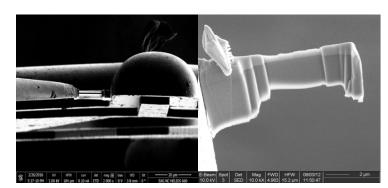

Using conventional FIB sample preparation procedures, extract a thin section from the area of interest, weld it to an Omnigrid and thin it to electron transparency (< 100 nm). Make sure the sample is attached to the correct (i.e. flat) side of the post, as shown in the Figure 1 left.

**Figure 1. Left:** Lamella in contact with the correct side of the post. trench, ready to be lifted out. **Right:** Lamella thinned to electron transparency after being welded to the side of a post of an Omnigrid. trench, ready to be lifted out.

After the lamella is thinned to electron transparency, ion-beam should be used sparingly since it damages the sample and introduces unwanted defects and amorphizaiton. (Tip: If using an FEI instrument, press F7 to use the "reduced area" window option, which can prevent ion-beam damage on the thinned part of the lamella). Place the "reduced area" window away from the region of interest to limit the viewing area and ion-beamexposed regions. E-beam imaging and deposition (of Pt, W, etc.) is recommended for welding and securing the sample.

### 2. Align E-chip and Omnigrid

Vent the SEM chamber and remove the Omnigrid from the stub. Lay down the Omnigrid and E-chips next to each other on one stub. Make sure the flat side of the Omnigrid (indicated in Figure 2) faces up. Insert the Omniprobe and bring it into contact with the lamella, as shown in Figure 2. Weld the lamella to the Omniprobe.

Figure 2. Left: Omnigrid is laid down with the flat side up, as indicated. Right: Omniprobe is in contact with the lamella.

### 3. Cut The Lamella Free

Vent the SEM chamber and remove the Omnigrid from the stub.

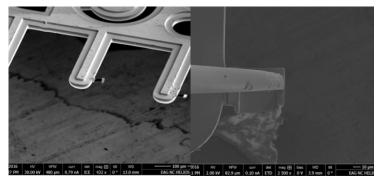

**Figure 3.** Cut the lamella free from the Omnigrid after lamella is attached to the Omniprobe.

### 4. Transfer to E-chip

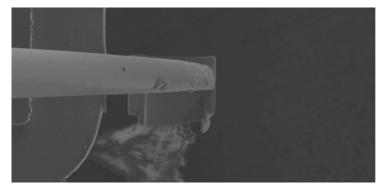

Use care when bringing the lamella into contact with the E-chip. Note that ion-beam not only damages the sample, but can also mill the thin SiN membrane. Therefore, e-beam imaging and deposition is highly recommended. Once the sample is in contact with the E-chip, Figure 4, the touch alarm and/or sudden change in contrast will occur. When using a thermal E-chip, align the sample so that the area of interest is over a hole in the ceramic membrane. For Electrical E-chips the sample can be placed over a hole in the membrane when applicable, but it should always be near the electrical leads so electrical contact can easily be made.

**Figure 4.** Lamella in contact with the heating membrane of the E-chip.

### 5. Secure the Sample

Once the sample is aligned with a hole, it can be welded in place. This helps with heat transfer from the heating membrane to the sample as well as image stability at elevated temperature.

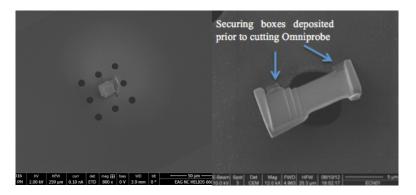

### 6. Cut the Omniprobe Free

Using ion-beam, cut the Omniprobe free and retract it to its park position. Figure 5 represents secured samples.

Note, low-kv thinning can be carried out at this step to thin the sample further. This will also remove any unwanted Pt deposition that may have occurred during the transferring or securing steps. To do so, tilt the stage to 52° or the angle needed in order to thin the sample further. Keep in mind; extensive thinning at this stage can lead to cutting the membrane. Cutting (burning holes) in the heating membrane can cause deviation in heating performance of the E-chips, since the current path can be different. In case of an electrical E-chip, burning holes in the SiN membrane does not affect the performance.

**Figure 5.** Secured samples. Omniprobe was cut free after the lamella was secured to the E-chip.

## Ex-Situ Lift-Out Method

Ex situ lift-out tools utilize a glass rod and electrostatic force to transfer lamella from the substrate to the E-chip

outside the FIB chamber. While these tools can be costly and require extra space in the lab, sample transfer is usually faster, cleaner and easier than the in situ lift out method described above.

### For conventional FIB lift-out geometries:

- 1. Follow the conventional FIB procedure to thin the sample to electron transparency. Cut and release the lamella from the substrate. Note, multiple samples can be prepared in parallel.

- 2. Remove the substrate from the FIB chamber.

- 3. Use an ex situ tool to lift out the sample from the substrate and position it on the E-chip membrane.

- If using a thermal E-chip, ensure the area of interest is over a hole in the ceramic membrane. Using an electrical E-chip, ensure the lamella is aligned with and near the electrical leads to allow for short electrical contacts.

- 5. The sample will adhere to the membrane via electrostatic forces and extra FIB pads are not necessary, as opposed to the in-situ methods. However, it is recommended to put the E-chip back in the FIB and deposit large pads (width of 0.5  $\mu$ m and height of 0.2  $\mu$ m) of Pt or W on both sides of the sample, preferably using e-beam deposition.

### For Ion-milled 3 mm disk samples

Lay the ion milled sample and an E-chip down inside the FIB. Cut a small section from the thinned area of the sample. Using an in situ or ex situ lift-out tool, transfer the section onto the E-chip. The flat side of the section should be in the same orientation as the E-chip membrane. For better electrical connection as well as heat transfer, it is recommended to deposit pads on the sample after this step, using e-beam deposition in FIB.

### Pt and W Contamination Concerns

Pt contamination can lead to shorting between the electrical contacts as well as unwanted reactions. If care is not taken Pt can form a thin layer over and around the lamella. This is due to either 1) imaging immediately after depositing pads, and/or 2) backscattered electrons (BSEs).

### **1. Imaging After Depositing Pads**

After depositing Pt or W pads, the gas flow is automatically stopped or the GIS needle is retracted. However, there are still gas precursor molecules present in the SEM chamber. Therefore, imaging immediately after the deposition will result in unwanted Pt or W deposition. Therefore, after deposition of pads and before imaging, ensure the chamber vacuum returns to the low E-6 Torr range, which, depending on the instrument, can take 5-10 minutes. Ideally, the chamber should be vented without imaging after pads are deposited.

#### 2. Backscattered Electrons

BSEs form as a result of e-beam interaction with the sample, and can be generated during metal deposition. While BSEs are unavoidable, they can be minimized by using lower accelerating voltages. In case of an electrical experiment, one can make a cut in the SiN layer, between and along the electrical pads.

### **Electrical Connections**

For electrical experiments, minimal contact resistance between the FIB deposited contacts and the sample is desired. FIB deposited contacts, via ion-beam-induced deposition (IBID) or electron-beam-induced deposition (EBID), have higher resistivity compared to bulk Pt (10  $\mu\Omega$ .cm), and IBID Pt is generally two orders of magnitude more electrically conductive than EBID Pt. However, Ga contamination and ion-beam damage are two major

concerns when using IBID. EBID has low conductivity due to presence of excess carbon contaminations compared to IBID, which come from the Pt precursor. There are two main approaches to enhance the conductivity of the EBIDs:

- Increase the accelerating voltage to 30 kV and focus the electron beam on the as-deposited pad for ~10min. High e-beam bombardment of the Pt pad will reduce the C content in the as-deposited Pt and increases the conductivity.

- After deposition, anneal the sample in an oxygen rich environment at 300 °C for ~10min, or at a lower temperature or different gas depending on the sample. This will remove the majority of the C content, and increase the conductivity.

The table below compares the resistivity between EBID and IBID contacts, and shows the conductivity enhancement measured after using the above approaches. Similar dimensions were used for this comparison, where L=16 µm, cross section=1µm<sup>2</sup>.

| Resistivity             | EBID (μΩ.cm) | IBID (μΩ.cm) |

|-------------------------|--------------|--------------|

| As-deposited            | ~3.75E3      | ~25          |

| Electron beam bombarded | ~min         | ~27          |

| Heated for 10 min       | 90           | ~25          |

There are contaminations concerns which need to be kept in mind:

- Focusing e-beam on the as-deposited pads results in deposition on contamination, which can result in contaminating the e-transparent and imaging area.

- Depending on the sample, heating under O-rich environment may lead to unwanted reactions such as oxidations or annealing of the sample.

- IBID introduces Ga contamination in the sample and may lead to unwanted reactions and amorphizaiton.

### References

[1] Straubinger, R., et al. "Preparation and Loading Process of Single Crystalline Samples into a Gas

Environmental Cell Holder for In Situ Atomic Resolution Scanning Transmission Electron Microscopic

Observation." Microscopy and microanalysis: the official journal of Microscopy Society of America, Microbeam

Analysis Society, Microscopical Society of Canada

(2016): 1-5.

[2] Hammad Fawey, Mohammed, et al. "In situ TEM studies of micron-sized all-solid-state fluoride ion batteries: Preparation, prospects, and challenges." Microscopy research and technique (2016).